BiSS and SPI are two common serial communication protocols used in industry, particularly in motor encoders and sensors. Although they may appear similar externally, there are key differences in their design goals, operating principles, and characteristics.

In short:

- SPI is a universal, simple, and widely used industrial standard communication bus.

- BiSS is an open protocol specifically designed for real-time sensors (such as absolute encoders), aiming to provide highly reliable, high-speed, and high-precision data exchange.

Below, we will compare them in detail across several parameters.

General Comparison

| Characteristic | BiSS Protocol | SPI Protocol |

|---|---|---|

| Protocol Nature | Open, point-to-point, master/slave | De facto standard, universal, master/slave |

| Design Goal | Specifically designed for real-time sensor data transmission with high safety requirements (e.g., encoders) | Universal, short-distance, board-level peripheral communication |

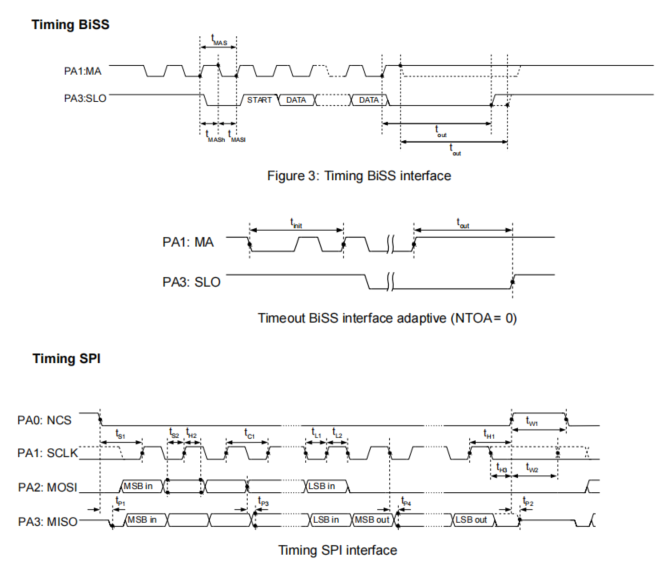

| Clock Mode | Unidirectional continuous clock (MASTER→SLAVE). The clock is active only during data transmission. | Bidirectional clock. The master generates the clock, but the slave can output data on the clock edge. |

| Data Frame Structure | Strictly defined frame structure, including start bit, data bits, CRC bits, status bits, etc. | No fixed frame structure. Data format and length are entirely defined by the master and slave device software. |

| Error Detection | Mandatory CRC (Cyclic Redundancy Check), providing powerful error detection critical for safety applications. | Typically no hardware-level error detection. Reliability depends on higher signal quality or software checks. |

| Slave Feedback | Dedicated unidirectional feedback line (SLO→MAS), completely separate from the clock line. | Bidirectional data line (MISO), master and slave share a common clock line. |

| Real-Time Performance | Deterministic delay. The delay between receiving the master’s clock and sending data is fixed and predictable. | Delay is non-deterministic, depends on the slave’s internal logic processing. |

| Application Field | High-performance absolute encoders, linear scales, servo drives, and other scenarios with high reliability and real-time requirements. | Flash memory, ADC/DAC converters, sensors, touchscreens, and other universal peripheral devices. |

Detailed Analysis of Differences

1. Physical Layer and Connection Method

- SPI: Uses 4 wires:

- SCLK (Serial Clock): Clock signal generated by the master.

- MOSI (Master Out Slave In): Data line for transmission from master to slave.

- MISO (Master In Slave Out): Data line for transmission from slave to master.

- CS (Chip Select): Chip select signal used by the master to select a specific slave device.

- BiSS: Also uses 4 wires, but the names and meanings differ slightly:

- MA (Master Clock): Equivalent to SPI’s SCLK, the clock signal from the master.

- SLO (Slave Out): Equivalent to SPI’s MISO, the slave output data line.

- SLI (Slave In): Used in some BiSS modes (e.g., register access), equivalent to SPI’s MOSI.

- nCS (Chip Select): Chip select signal, functionally similar to SPI’s CS.

Note: In the simplest BiSS C address-free mode (often used in encoders), the SLI line is not needed; only MA, SLO, and nCS wires are required. This is the basis for its physical compatibility with SPI.

2. Data Transmission Mechanism (Key Difference)

This is the most fundamental difference, determining their application areas.

- SPI Communication Process:

- The master pulls the CS signal of the corresponding slave device low.

- The master starts generating the SCLK clock.

- The master simultaneously sends data (usually commands or addresses) to the slave via the MOSI line.

- The slave simultaneously returns data to the master via the MISO line.

- Communication ends, the master pulls the CS signal high.

Characteristics: Full-duplex, simultaneous transmission and reception. Data content, length, and meaning are entirely defined by the device manufacturer.

- BiSS Communication Process:

- The master pulls the nCS signal low, marking the start of a communication frame.

- The master generates a fixed number of MA clock pulses (e.g., 64 pulses for a 64-bit frame).

- In the first few clock cycles, the slave (encoder) sends a fixed “start bit” and “sensor status bits” via the SLO line.

- In subsequent clock cycles, the slave sends the core position data.

- At the end of the frame, the slave sends a CRC checksum.

- After receiving the entire frame, the master calculates the CRC and compares it with the received one to verify data correctness.

- The master pulls the nCS signal high, ending the frame.

Characteristics: Half-duplex, with a strict, predefined frame structure. The master sends the clock to “read” data without sending commands on the data line (in address-free mode). The entire process is deterministic.

3. Error Detection and Reliability

- BiSS: Built-in CRC check is a mandatory part of the protocol. This ensures very high reliability of data transmission in complex industrial electromagnetic environments (e.g., near frequency converters, motors). If the CRC check fails, the master can immediately discard the data, which is a functional safety requirement.

- SPI: The protocol itself does not contain any error detection mechanisms. If the application requires it, it must be implemented additionally at the software level (e.g., adding a checksum to the transmitted data), but this increases overhead and is non-standard.

Summary and Selection Recommendations

| Scenario | Recommended Protocol | Reasoning |

|---|---|---|

| Connecting Flash memory, ADC, ordinary sensors | SPI | Simple, universal, supported by many manufacturers, rich resources for developers. |

| High-performance absolute encoders in servo drives | BiSS | High reliability, deterministic delay, built-in CRC check, optimized for real-time control. |

| System requires functional safety certification (e.g., SIL/ISO13849) | BiSS | Its built-in safety mechanisms (CRC) facilitate compliance with certification requirements. |

| Replacement or compatibility with traditional incremental encoders (A/B/Z) | BiSS | The BiSS interface can directly output analog A/B/Z signals, simplifying system upgrades. |

| Hardware configuration is fixed, simple data reading is required | Both | Many BiSS encoders offer an “SPI compatibility mode,” allowing reading via an SPI controller, but losing the benefits of BiSS’s CRC and determinism. |

Important Note: Since BiSS is physically compatible with SPI, many BiSS encoders can be switched to “SPI mode” for reading using a standard SPI interface. However, this is only a compatibility mode. In this mode, you are using the SPI communication mechanism and do not benefit from the native BiSS protocol’s CRC check and strict timing reliability. In true applications with high safety requirements, a genuine BiSS host controller should be used.